# 25 MBPS Quad-Channel Digital Isolator

ADuM7442S

#### 1.0 Scope

This specification documents the detailed requirements for space qualified products manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein.

The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. <a href="http://www.analog.com/aeroinfo">http://www.analog.com/aeroinfo</a>

This data specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="http://www.analog.com/ADuM7442">http://www.analog.com/ADuM7442</a>

#### 2.0 Part Number

The complete part number(s) of this specification follows:

Specific Part Number Description

ADuM7442R703F 25 MBPS Quad-Channel Digital Isolator

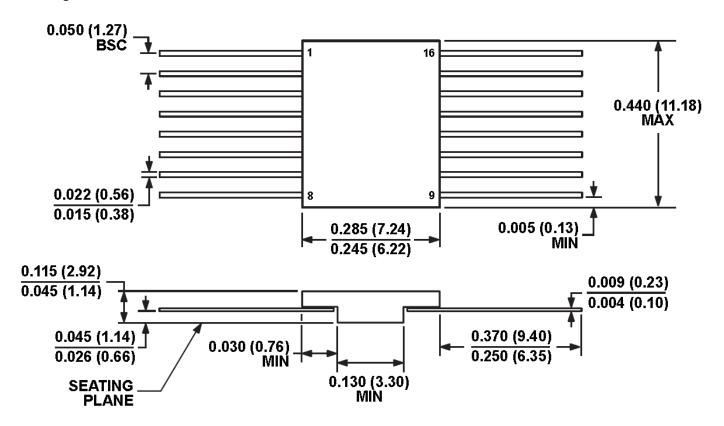

## 3.0 Case Outline

The case outline(s) are as designated in MIL-STD-1835 and as follows:

<u>Outline Letter</u> <u>Descriptive Designator</u> <u>Terminals</u> <u>Lead Finish</u> <u>Package style</u>

X CDFP4-F16 16-Lead Hot Solder Dip Bottom Brazed Flat Pack

Tel: 800.262.5643

| Package: X |                    |                |                                                                       |  |  |  |  |

|------------|--------------------|----------------|-----------------------------------------------------------------------|--|--|--|--|

| Pin Number | Terminal<br>Symbol | Pin Type       | Pin Description                                                       |  |  |  |  |

| 1          | V <sub>DD1A</sub>  | Power          | Supply Voltage A for Isolator Side 1. 1/, 2/                          |  |  |  |  |

| 2          | GND₁               | Power          | Ground 1. Ground reference for Isolator Side 1. 3/, 6/                |  |  |  |  |

| 3          | VIA                | Digital Input  | Logic Input A                                                         |  |  |  |  |

| 4          | $V_{IB}$           | Digital Input  | Logic Input B                                                         |  |  |  |  |

| 5          | Voc                | Digital Output | Logic Output C                                                        |  |  |  |  |

| 6          | $V_{OD}$           | Digital Output | Logic Output D                                                        |  |  |  |  |

| 7          | $V_{DD1B}$         | Power          | Supply Voltage B for Isolator Side 1. <u>1</u> /, <u>2</u> /          |  |  |  |  |

| 8          | GND₁               | Power          | Ground 1. Ground reference for Isolator Side 1. <u>3</u> / <u>6</u> / |  |  |  |  |

| 9          | $GND_2$            | Power          | Ground 2. Ground reference for Isolator Side 2. 4/                    |  |  |  |  |

| 10         | $V_{\text{DD2B}}$  | Power          | Supply Voltage B for Isolator Side 2. <u>2</u> /, <u>5</u> /          |  |  |  |  |

| 11         | $V_{ID}$           | Digital Input  | Logic Input D                                                         |  |  |  |  |

| 12         | $V_{IC}$           | Digital Input  | Logic Input C                                                         |  |  |  |  |

| 13         | $V_{OB}$           | Digital Output | Logic Output B                                                        |  |  |  |  |

| 14         | $V_{OA}$           | Digital Output | Logic Output A                                                        |  |  |  |  |

| 15         | GND <sub>2</sub>   | Power          | Ground 2. Ground reference for Isolator Side 2. <u>4</u> /            |  |  |  |  |

| 16         | $V_{\text{DD2A}}$  | Power          | Supply Voltage A for Isolator Side 2. <u>2</u> /, <u>5</u> /          |  |  |  |  |

| Lid        |                    | Power          | Metal Lid electrically connected to ground. (GND <sub>1</sub> )       |  |  |  |  |

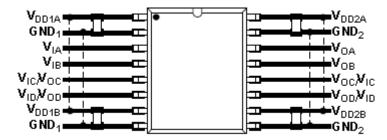

Figure 1 - Terminal Connections

<sup>1/2</sup> Pin 1 must be connected externally to Pin 7. 1/2 Connect a ceramic bypass capacitor of value 0.01  $\mu$ F to 0.1  $\mu$ F between  $V_{DD1A}$  (Pin 1) and GND<sub>1</sub> (Pin 2), between  $V_{DD1B}$  (Pin 7) and GND<sub>1</sub> (Pin 8), Z/ Connect a ceramic bypass capacitor of Value 0.01 µF to 0.1 µF between V<sub>DD1A</sub> (Pin 1) and between V<sub>DD2B</sub> (Pin 10) and GND<sub>2</sub> (Pin 9), and between V<sub>DD2A</sub> (Pin 16) and GND<sub>2</sub> (Pin 15).

3/ Pin 2 and Pin 8 are internally connected, and connecting both to GND<sub>1</sub> is recommended.

4/ Pin 9 and Pin 15 are internally connected, and connecting both to GND<sub>2</sub> is recommended.

5/ Pin 10 must be connected externally to Pin 16.

6/ Internally connected to Metal Lid.

#### 4.0 Specifications

| <sub>02</sub> )0.5V to 7.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ., V <sub>ID</sub> )0.5V to V <sub>DDI</sub> + 0.5V <u>2</u> / <u>3</u> /                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Voc, VoD)0.5V to VDDO + 0.5V2/ $\underline{3}$ /                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ge65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| o <sub>1</sub> , lo <sub>2</sub> )10mA to +10mA                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ximum (T <sub>J</sub> ) +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ering, 60 seconds) +300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| tion-to-case (θυς) 60 °C/W <u>4</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tion-to-ambient (θ <sub>JA</sub> ) 98 °C/W <u>4</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| g Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| +3.3 V to +5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| erature range (T <sub>A</sub> )55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ormance Characteristics 5/                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6pF <u>8</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ge       -65°C to +150°C         o1, lo2)       -10mA to +10mA         aximum (TJ)       +150°C         ering, 60 seconds)       +300°C         tion-to-case (θJC)       60 °C/W 4/         tion-to-ambient (θJA)       98 °C/W 4/         g Conditions       +3.3 V to +5.0 V         erature range (TA)       -55°C to +125°C         ormance Characteristics 5/       2ns         1.2 Mbps         V       1.1 Mbps         t Immunity  CM        15 kV/μs 6/         utput)       10pF 7/ |

## 4.4 Radiation Features

Maximum total dose available (dose rate = 50 – 300 rads (Si)/s) ....100 k rads (Si)

<sup>1/</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

<sup>2/</sup> V<sub>DDI</sub> and V<sub>DDO</sub> refer to the supply voltages on the input and output sides of a given channel, respectively. See the PC Board Layout section.

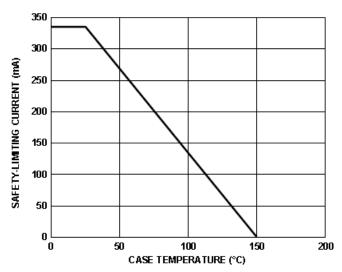

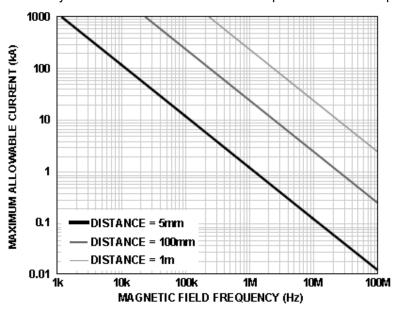

<sup>3/</sup> See Figure 2 for maximum rated current values for various temperatures.

<sup>4/</sup> Measurement taken under absolute worst-case condition and represent data taken with thermal camera for highest power density location. See MIL-STD-1835 for average O<sub>JC</sub> number.

<sup>5</sup>/ All typical specifications are at TA = 25°C, V<sub>DD1</sub> All typical specifications are at TA = 25°C, 3.6 V  $\leq$  V<sub>DD1</sub>  $\leq$  5. V, 3.3 V  $\leq$  V<sub>DD2</sub>  $\leq$  5.0 V, unless otherwise noted. Switching specifications are tested with CL = 15 pF and CMOS signal levels, unless otherwise noted.

<sup>6/ |</sup>CM| is the maximum common-mode voltage slew rate that can be sustained while maintaining Vo > 0.8 VDD, VIx = VDDx, VCM = 200 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

<sup>7/</sup> The device is considered a 2-terminal device: Pin 1 through Pin 8 is shorted together and Pin 9 through Pin 16 are shorted together.

<sup>8/</sup> Input capacitance is from any input data pin to ground.

TABLE IA – ELECTRICAL PERFORMANCE CHARACTERISTICS - 5V OPERATION

| Parameter<br>See notes at end of table                    | Symbol                              | Conditions <u>1</u> /<br>Unless otherwise specified                             | Sub-Group | Limit<br>Min           | Limit<br>Max         | Units    |

|-----------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|-----------|------------------------|----------------------|----------|

| SWITCHING CHARACTERISTICS                                 | ı                                   |                                                                                 |           |                        |                      | <u>l</u> |

| Data Rate                                                 | DR                                  | Within PWD Limit                                                                | 9,10,11   |                        | 25                   | Mbps     |

|                                                           |                                     | M,D,P,L,R                                                                       | 9         |                        | 25                   | Mbps     |

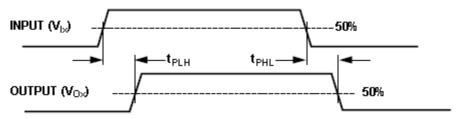

| Propagation Delay                                         | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50% output                                                         | 9,10,11   | 29                     | 50                   | ns       |

| 1,13.11                                                   |                                     | M,D,P,L,R                                                                       | 9         | 29                     | 50                   | ns       |

| Pulse Width Distortion                                    | PWD                                 | t <sub>PLH</sub> - t <sub>PHL</sub>                                             | 9,10,11   | -                      | 5                    | ns       |

|                                                           |                                     | M,D,P,L,R                                                                       | 9         |                        | 5                    | ns       |

| Pulse Width                                               | PW                                  | Within PWD limit                                                                | 9,10,11   | 40                     |                      | ns       |

|                                                           |                                     | M,D,P,L,R                                                                       | 9         | 40                     |                      | ns       |

| Propagation Delay Skew <u>2</u> /, <u>3</u> /, <u>4</u> / | t <sub>PSK</sub>                    | , , , , ,                                                                       | 9,10,11   |                        | 10                   | ns       |

| Pulse Width Distortion                                    | ΔPWD                                |                                                                                 | 10,11     |                        | 30                   | ps/°C    |

| Change vs. Temperature <u>3</u> /                         |                                     |                                                                                 |           |                        |                      | ρυ, σ    |

| Channel Matching                                          | <b>t</b> <sub>PSKCD</sub>           |                                                                                 | 9,10,11   |                        | 4                    | ns       |

| Codirection                                               | 1, 5,1,0,5                          | M,D,P,L,R                                                                       | 9         |                        | 4                    | ns       |

| Channel Matching                                          | <b>t</b> <sub>PSKOD</sub>           |                                                                                 | 9,10,11   |                        | 6                    | ns       |

| Opposing-Direction                                        | 11 511.05                           | M,D,P,L,R                                                                       | 9         |                        | 6                    | ns       |

| SUPPLY CURRENT                                            | l                                   |                                                                                 |           |                        | <u> </u>             | 1        |

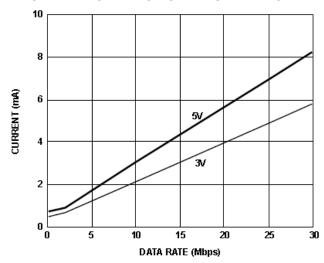

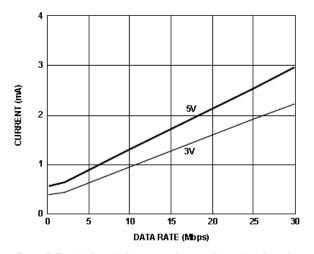

| Dynamic Supply Current                                    | I <sub>DD1(D)</sub>                 | F = 2MBPS, 10MBPS, 25MBPS                                                       | 4, 5      |                        | 20                   | mA       |

| zynamie zappiy zameni                                     | 1001(0)                             | 22. 3, 102. 3, 202. 3                                                           | 6         |                        | 22                   | mA       |

|                                                           |                                     | M,D,P,L,R                                                                       | 4         |                        | 20                   | mA       |

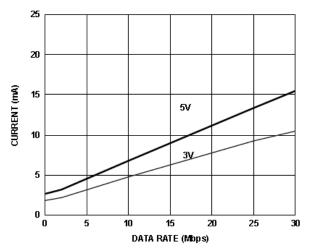

|                                                           | I <sub>DD2(D)</sub>                 | F = 2MBPS, 10MBPS, 25MBPS                                                       | 4, 5      |                        | 20                   | mA       |

|                                                           | 1002(0)                             | 211151 3, 1011151 3, 2311151 3                                                  | 6         |                        | 22                   | mA       |

|                                                           |                                     | M,D,P,L,R                                                                       | 4         |                        | 20                   | mA       |

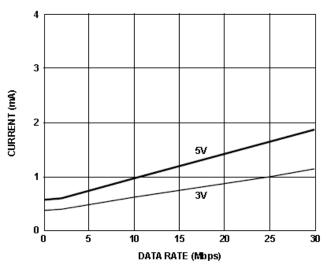

| Quiescent Supply Current                                  | I <sub>DD1(Q)</sub>                 | 111,071 12,11                                                                   | 1,2,3     |                        | 3.8                  | mA       |

| Quiescent supply current                                  | IDDI(Q)                             | M,D,P,L,R                                                                       | 1         |                        | 3.8                  | mA       |

|                                                           | I <sub>DD2(Q)</sub>                 | 111,071 12,11                                                                   | 2         |                        | 2.92                 | mA       |

|                                                           | 1002(Q)                             |                                                                                 | 1,3       |                        | 3.4                  | mA       |

|                                                           |                                     | M,D,P,L,R                                                                       | 1         |                        | 3.4                  | mA       |

| DC CHARACTERISTICS                                        | 1                                   | 111,071 12,11                                                                   |           |                        | 3                    | 11171    |

| Logic High Input Threshold                                | VIH                                 | 7/                                                                              | 1,2,3     | 0.7 V <sub>DDx</sub>   |                      | V        |

| Logic riigii iripat riii esiioid                          | <b>V</b>                            | M,D,P,L,R                                                                       | 1         | 0.7 V <sub>DDx</sub>   |                      | V        |

| Logic low Input Threshold                                 | VIL                                 | <u>7</u> /                                                                      | 1,2,3     | 0.7 VDDx               | 0.3 V <sub>DDx</sub> | V        |

| Logic low input The Shora                                 | V.L                                 | M,D,P,L,R                                                                       | 1,2,3     |                        | 0.3 V <sub>DDx</sub> | V        |

| Logic High Output Voltages                                | VOH                                 | $I_{Ox} = -20 \mu\text{A},  V_{Ix} = V_{IxH}  \frac{5}{2} /,  \frac{6}{7} /$    | 1,2,3     | V <sub>DDx</sub> - 0.1 | 0.5 V DDX            | V        |

| Logic riigii output voitages                              | 1011                                | ·                                                                               |           |                        |                      |          |

|                                                           |                                     | M,D,P,L,R                                                                       | 1         | V <sub>DDx</sub> - 0.1 |                      | V        |

|                                                           |                                     | $I_{Ox} = -4 \text{ mA}, V_{Ix} = V_{IxH} \frac{5}{5}, \frac{6}{7}$             | 1,2,3     | V <sub>DDx</sub> - 0.4 |                      | V        |

|                                                           | 1/01                                | M,D,P,L,R                                                                       | 1         | V <sub>DDx</sub> - 0.4 | 0.1                  | V        |

| Logic Low Output Voltages                                 | VOL                                 | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{IxL} 5/, 6/,7/$                              | 1,2,3     |                        | 0.1                  | V        |

|                                                           |                                     | M,D,P,L,R                                                                       | 1         |                        | 0.1                  | V        |

|                                                           |                                     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL} \frac{5}{5}, \frac{6}{5}, \frac{7}{5}$ | 1,2,3     |                        | 0.4                  | V        |

|                                                           | <b>_</b>                            | M,D,P,L,R                                                                       | 1         | 4.0                    | 0.4                  | V        |

| Input Leakage Current per                                 | I <sub>IH</sub>                     | $V_{lx} = V_{DDx} 5/, 6/,7/$                                                    | 1,2,3     | -10                    | +10                  | μA       |

| Channel                                                   | <u> </u>                            | M,D,P,L,R                                                                       | 1         | -10                    | +10                  | μΑ       |

|                                                           | I <sub>IL</sub>                     | $V_{1x} = 0V \ \underline{5}/, \underline{6}/,\underline{7}/$                   | 1,2,3     | -10                    | +10                  | μΑ       |

| ACCILIADA CTEDISTICO                                      | 1                                   | M,D,P,L,R                                                                       | 1         | -10                    | +10                  | μΑ       |

| AC CHARACTERISTICS                                        |                                     |                                                                                 |           |                        |                      |          |

| Output Rise/Fall Time 2/, 3/                              | t <sub>R</sub> /t <sub>F</sub>      | 10% to 90%                                                                      | 4         |                        | 2.5                  | ns       |

|                                                           |                                     |                                                                                 | 5         |                        | 3                    |          |

|                                                           | 1                                   |                                                                                 | 6         |                        | 2                    | 1        |

# TABLE IA NOTES:

- 1/TA nom = 25°C, TA max = 125°C, and TA min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted.  $V_{DDx}$  nom = 5 V,  $V_{DDx}$  max = 5.5V,  $V_{DDx}$  min = 4.5V.

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation.

- 4/ t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ V<sub>Ix</sub> refers to the voltage input signals of a given channel (A, B, C, or D).

- 6/ I<sub>Ox</sub> refers to the output current of a given channel (A, B, C, or D).

- 7/ V<sub>DDx</sub> refers to the power supply on either side of a given channel (A, B, C, or D).

TABLE IB - ELECTRICAL PERFORMANCE CHARACTERISTICS - 3.3V OPERATION

| Parameter                                                    | Symbol                              | Conditions 1/                                                      | Sub-    | Limit                | Limit                | Units    |

|--------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------|---------|----------------------|----------------------|----------|

| See notes at end of table                                    |                                     | Unless otherwise specified                                         | Group   | Min                  | Max                  |          |

| SWITCHING CHARACTERISTI                                      |                                     | hart sugar                                                         |         |                      |                      |          |

| Data Rate                                                    | DR                                  | Within PWD Limit                                                   | 9,10,11 |                      | 25                   | Mbps     |

|                                                              |                                     | M,D,P,L,R                                                          | 9       | 20                   | 25                   | Mbps     |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50% output                                            | 9,10,11 | 29                   | 66                   | ns       |

| D. J W. Jak. D                                               | מאים                                | M,D,P,L,R                                                          | 9       | 29                   | 66                   | ns       |

| Pulse Width Distortion                                       | PWD                                 | t <sub>PLH</sub> - tP <sub>HL</sub>                                | 9,11    |                      | 5                    | ns       |

|                                                              |                                     |                                                                    | 10      |                      | 9                    |          |

|                                                              |                                     | M,D,P,L,R                                                          | 9       |                      | 5                    | ns       |

| Pulse Width                                                  | PW                                  | Within PWD limit                                                   | 9,10,11 | 40                   |                      | ns       |

|                                                              |                                     | M,D,P,L,R                                                          | 9       | 40                   |                      | ns       |

| Propagation Delay<br>Skew <u>2</u> /, <u>3</u> /, <u>4</u> / | t <sub>PSK</sub>                    |                                                                    | 9,10,11 |                      | 10                   | ns       |

| Pulse Width Distortion<br>Change vs. Temperature <u>3</u> /  | ΔPWD                                |                                                                    | 10,11   |                      | 43                   | ps/°C    |

| Channel Matching                                             | t <sub>PSKCD</sub>                  |                                                                    | 9,10,11 |                      | 5                    | ns       |

| Codirection                                                  |                                     | M,D,P,L,R                                                          | 9       |                      | 5                    | ns       |

| Channel Matching                                             | <b>t</b> PSKOD                      |                                                                    | 9,10,11 |                      | 7                    | ns       |

| Opposing-Direction                                           |                                     | M,D,P,L,R                                                          | 9       |                      | 7                    | ns       |

| SUPPLY CURRENT                                               |                                     | <del>.</del>                                                       | •       | •                    |                      |          |

| Dynamic Supply Current                                       | I <sub>DD1(D)</sub>                 | F = 2MBPS, 10MBPS, 25MBPS                                          | 4       |                      | 13                   | mA       |

|                                                              |                                     |                                                                    | 5,6     |                      | 14                   |          |

|                                                              |                                     | M,D,P,L,R                                                          | 4       |                      | 13                   | mA       |

|                                                              | I <sub>DD2(D)</sub>                 | F = 2MBPS, 10MBPS, 25MBPS                                          | 4,5     |                      | 13                   | mA       |

|                                                              | *DD2(D)                             | 211151 3, 1011151 3, 2311151 3                                     | 6       |                      | 15                   | 1117     |

|                                                              |                                     | M,D,P,L,R                                                          | 4       |                      | 13                   | mA       |

| Quiescent Supply                                             | 1                                   | IVI,D,P,L,R                                                        | 1,2,3   |                      | 2.4                  |          |

| Current                                                      | DD1(Q)                              | M,D,P,L,R                                                          | 1 .     |                      | 2.4                  | mA<br>mA |

| Current                                                      | I                                   | IVI,D,P,L,R                                                        | 1,2     |                      | 2.4                  | mA<br>mA |

|                                                              | DD2(Q)                              |                                                                    |         |                      |                      |          |

|                                                              |                                     |                                                                    | 3       |                      | 2.4                  | mA       |

| DC CHARACTERISTICS                                           |                                     | M,D,P,L,R                                                          | 1       |                      | 2.3                  | mA       |

| Logic High Input                                             | VIH                                 | 7/                                                                 | 1 2 2   | 0.7 V <sub>DDx</sub> |                      | V        |

| Threshold                                                    | VIII                                | <u>7</u> /                                                         | 1,2,3   | 0.7 V <sub>DDx</sub> |                      | V        |

| Logic low Input Threshold                                    | VIL                                 | M,D,P,L,R                                                          | · ·     | U.7 V <sub>DDx</sub> | 0.3 V <sub>DDx</sub> | V        |

| Logic low input Threshold                                    | VIL                                 |                                                                    | 1,2,3   |                      | 0.3 V <sub>DDx</sub> | V        |

| Lasia Iliah Outout                                           | VOH                                 | $M,D,P,L,R$ $I_{Ox} = -20 \mu A, V_{Ix} = V_{IxH} 5/, 6/,7/$       | 1 2 2   | V 0.1                | U.3 V <sub>DDx</sub> | V        |

| Logic High Output<br>Voltages                                | VOH                                 |                                                                    | 1,2,3   | $V_{DDx} - 0.1$      |                      | -        |

| voitages                                                     |                                     | M,D,P,L,R                                                          | 1       | $V_{DDx} - 0.1$      |                      | V        |

|                                                              |                                     | $I_{Ox} = -4 \mu A, V_{Ix} = V_{IxH} 5/, 6/,7/$                    | 1,2,3   | $V_{DDx} - 0.4$      |                      | V        |

|                                                              |                                     | M,D,P,L,R                                                          | 1       | $V_{DDx} - 0.4$      |                      | V        |

| Logic Low Output                                             | VOL                                 | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{IxL} 5/, 6/,7/$                 | 1,2,3   |                      | 0.1                  | V        |

| Voltages                                                     |                                     | M,D,P,L,R                                                          | 1       |                      | 0.1                  | V        |

|                                                              |                                     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL} \frac{5}{6}, \frac{6}{7}$ | 1,2,3   |                      | 0.4                  | V        |

|                                                              |                                     | M,D,P,L,R                                                          | 1       |                      | 0.4                  | V        |

| Input Leakage Current per                                    | I <sub>IH</sub>                     | $V_{ix} = V_{DDx} \underline{5}/, \underline{6}/,\underline{7}/$   | 1,2,3   | -10                  | +10                  | μΑ       |

| Channel                                                      |                                     | M,D,P,L,R                                                          | 1       | -10                  | +10                  | μΑ       |

|                                                              | I₁∟                                 | $V_{lx} = 0V \ \underline{5}/, \underline{6}/,\underline{7}/$      | 1,2,3   | -10                  | +10                  | μΑ       |

|                                                              |                                     | M,D,P,L,R                                                          | 1       | -10                  | +10                  | μΑ       |

| AC CHARACTERISTICS                                           |                                     |                                                                    |         |                      |                      |          |

| Output Rise/Fall Time                                        | t <sub>R</sub> /t <sub>F</sub>      | 10% to 90%                                                         | 4       |                      | 3                    | ns       |

| <u>2</u> /, <u>3</u> /                                       |                                     |                                                                    | 5       |                      | 4                    |          |

|                                                              |                                     |                                                                    | 6       |                      | 2.5                  |          |

#### TABLE IB NOTES:

- 1/TA nom = 25°C, TA max = 125°C, and TA min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted.  $V_{DDx}$  nom = 3.3 V,  $V_{DDx}$  max = 3.6V,  $V_{DDx}$  min = 3V.

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation.

- 4/ t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ V<sub>Ix</sub> refers to the voltage input signals of a given channel (A, B, C, or D).

- 6/ I<sub>Ox</sub> refers to the output current of a given channel (A, B, C, or D).

- 7/ V<sub>DDx</sub> refers to the power supply on either side of a given channel (A, B, C, or D).

TABLE IC - ELECTRICAL PERFORMANCE CHARACTERISTICS - MIXED 5 V/3.3 V OPERATION

| Parameter                          | Symbol                              | Conditi                                                          |                                                     | Sub-    | Limit           | Limit         | Units        |

|------------------------------------|-------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|---------|-----------------|---------------|--------------|

| See notes at end of table          |                                     | Unless otherw                                                    | ise specified                                       | Group   | Min             | Max           |              |

| SWITCHING CHARACTERISTIC           |                                     | Mithin DMD Lineit                                                |                                                     | 0.10.11 |                 | 25            | A 41         |

| Data Rate                          | DR                                  | Within PWD Limit                                                 | M,D,P,L,R                                           | 9,10,11 |                 | 25<br>25      | Mbps<br>Mbps |

| Dropogotion Dolov                  |                                     | F00/ :                                                           |                                                     |         | 20              |               |              |

| Propagation Delay                  | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50%                                                 | ουιραι                                              | 9,11    | 30<br>30        | 55<br>57      | ns           |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 9       | 30              | 55            | ns           |

| Pulse Width Distortion             | PWD                                 | t <sub>PLH</sub> – tP <sub>HL</sub>                              | 1V1,D,1 ,L,11                                       | 9,11    | 30              | 5             | ns           |

| T dise Width Distortion            | IVVD                                | TOPEN — CI HE                                                    |                                                     | 10      |                 | 7             | 113          |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 9       |                 | 5             | nc           |

| Pulse Width                        | PW                                  | Within PWD limit                                                 | IVI,D,F,L,N                                         | 9,10,11 | 40              | J             | ns<br>ns     |

| r dise Width                       | 1 44                                | Within Wolling                                                   | M,D,P,L,R                                           | 9,10,11 | 40              |               | ns           |

| Propagation Delay Skew             | t <sub>PSK</sub>                    |                                                                  | IVI,D,I ,L,IX                                       | 9,10,11 | 70              | 10            | ns           |

| <u>2</u> /, <u>3</u> /, <u>4</u> / | -                                   |                                                                  |                                                     |         |                 | -             |              |

| Pulse Width Distortion             | $\Delta$ PWD                        |                                                                  |                                                     | 10,11   |                 | 40            | ps/°C        |

| Change vs. Temperature <u>3</u> /  |                                     |                                                                  |                                                     |         |                 | _             |              |

| Channel Matching                   | <b>t</b> PSKCD                      |                                                                  |                                                     | 9,10,11 |                 | 5             | ns           |

| Codirection                        |                                     |                                                                  | M,D,P,L,R                                           | 9       |                 | 5             | ns           |

| Channel Matching                   | t <sub>PSKOD</sub>                  |                                                                  |                                                     | 9,10    |                 | 9             | ns           |

| Opposing-Direction                 |                                     |                                                                  | MDDLD                                               | 11      |                 | 12            | ns           |

| SUPPLY CURRENT                     |                                     |                                                                  | M,D,P,L,R                                           | 9       |                 | 9             | ns           |

|                                    | 1                                   | T=                                                               |                                                     |         | 1               |               |              |

| Dynamic Supply Current             | I <sub>DD1(D)</sub>                 | F = 2MBPS, 10MB                                                  |                                                     | 4,5,6   |                 | 20            | mA           |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 4       |                 | 20            | mA           |

|                                    | I <sub>DD2(D)</sub>                 | F = 2MBPS, 10MBF                                                 | PS, 25MBPS                                          | 4,5     |                 | 12            | mA           |

|                                    |                                     |                                                                  |                                                     | 6       |                 | 15            |              |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 4       |                 | 12            | mA           |

| Quiescent Supply Current           | $I_{DD1(Q)}$                        |                                                                  |                                                     | 1,2,3   |                 | 3.8           | mA           |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       |                 | 3.8           | mA           |

|                                    | $I_{DD2(Q)}$                        |                                                                  |                                                     | 1,2     |                 | 2.3           | mA           |

|                                    |                                     |                                                                  |                                                     | 3       |                 | 2.4           | mA           |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       |                 | 2.3           | mA           |

| DC CHARACTERISTICS                 | 1                                   |                                                                  |                                                     |         |                 |               |              |

| Logic High Input Threshold         | VIH                                 | <u>7</u> /                                                       | _                                                   | 1,2,3   | $0.7 V_{DDx}$   |               | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       | $0.7 V_{DDx}$   |               | V            |

| Logic low Input Threshold          | VIL                                 | <u>7</u> /                                                       |                                                     | 1,2,3   |                 | $0.3 V_{DDx}$ | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       |                 | $0.3 V_{DDx}$ | V            |

| Logic High Output Voltages         | VOH                                 | $I_{Ox} = -20 \mu A, V_{Ix} = 1$                                 | V <sub>іхн</sub> <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3   | $V_{DDx} - 0.1$ |               | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       | $V_{DDx} - 0.1$ |               | V            |

|                                    |                                     | $I_{Ox} = -4 \mu A$ , $V_{Ix} = V_{I}$                           |                                                     | 1,2,3   | $V_{DDx} - 0.4$ | -             | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       | $V_{DDx} - 0.4$ |               | V            |

| Logic Low Output Voltages          | VOL                                 | $I_{Ox} = 20 \mu A, V_{Ix} = V_{Ix}$                             |                                                     | 1,2,3   |                 | 0.1           | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       |                 | 0.1           | V            |

|                                    |                                     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{Ix}$                         |                                                     | 1,2,3   |                 | 0.4           | V            |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       |                 | 0.4           | V            |

| Input Leakage Current per          | I <sub>IH</sub>                     | $V_{lx} = V_{DDx} \underline{5}/, \underline{6}/,\underline{7}/$ |                                                     | 1,2,3   | -10             | +10           | μΑ           |

| Channel                            |                                     |                                                                  | M,D,P,L,R                                           | 1       | -10             | +10           | μΑ           |

|                                    | I <sub>IL</sub>                     | $V_{1x} = 0V \ \underline{5}/, \underline{6}/, \underline{7}/$   |                                                     | 1,2,3   | -10             | +10           | μΑ           |

|                                    |                                     |                                                                  | M,D,P,L,R                                           | 1       | -10             | +10           | μΑ           |

| AC CHARACTERISTICS                 | ,                                   |                                                                  |                                                     |         |                 |               |              |

| Output Rise/Fall Time              | t <sub>R</sub> /t <sub>F</sub>      | 10% to 90%                                                       |                                                     | 4       |                 | 3             | ns           |

| <u>2</u> /, <u>3</u> /             |                                     |                                                                  |                                                     | 5       |                 | 4             |              |

|                                    |                                     |                                                                  |                                                     | 6       |                 | 2.5           |              |

#### TABLE IC NOTES:

- 1/ TA nom = 25°C, TA max = 125°C, and TA min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted.  $V_{DD1}$  nom = 5 V,  $V_{DD1}$  max = 5.5V,  $V_{DD1}$  min = 4.5V /  $V_{DD2}$  nom = 3.3 V,  $V_{DD2}$  max = 3.6V,  $V_{DD2}$  min = 3V

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation.

- 4/ tpsk is the magnitude of the worst-case difference in tphL or tpLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- $5/V_{lx}$  refers to the voltage input signals of a given channel (A, B, C, or D).

- 6/ I<sub>Ox</sub> refers to the output current of a given channel (A, B, C, or D).

- 7/ V<sub>DDx</sub> refers to the power supply on either side of a given channel (A, B, C, or D).

TABLE ID - ELECTRICAL PERFORMANCE CHARACTERISTICS - MIXED 3.3 V/5 V OPERATION

| Parameter<br>See notes at end of table                       | Symbol                              | Conditions <u>1</u> /<br>Unless otherwise specified                                                        | Sub-<br>Group | Limit<br>Min                                 | Limit<br>Max         | Units |

|--------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|----------------------|-------|

| SWITCHING CHARACTERIST                                       | ICS                                 | 2 mess other wise specified                                                                                | oup           | •••••                                        |                      | l     |

| Data Rate                                                    | DR                                  | Within PWD Limit                                                                                           | 9,10,11       |                                              | 25                   | Mbps  |

| Data nate                                                    |                                     | M,D,P,L,R                                                                                                  | 9             |                                              | 25                   | Mbps  |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50% output                                                                                    | 9,10,11       | 31                                           | 60                   | ns    |

| , ,                                                          | -                                   | M,D,P,L,R                                                                                                  | 9             | 31                                           | 60                   | ns    |

| Pulse Width                                                  | PWD                                 | t <sub>PLH</sub> - tP <sub>HL</sub>                                                                        | 9, 11         | <u> </u>                                     | 5                    | ns    |

| Distortion                                                   |                                     | [                                                                                                          | 10            |                                              | 7                    |       |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 9             |                                              | 5                    | ns    |

| Pulse Width                                                  | PW                                  | Within PWD limit                                                                                           | 9,10,11       | 40                                           |                      | ns    |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 9             | 40                                           |                      | ns    |

| Propagation Delay<br>Skew <u>2</u> /, <u>3</u> /, <u>4</u> / |                                     |                                                                                                            | 9,10,11       |                                              | 10                   | ns    |

| Pulse Width Distortion                                       | ΔPWD                                |                                                                                                            | 10,11         |                                              | 33                   | ps/°C |

| Change vs. Temperature <u>3</u> /                            |                                     |                                                                                                            |               |                                              |                      |       |

| Channel Matching                                             | <b>t</b> PSKCD                      |                                                                                                            | 9,10,11       |                                              | 5                    | ns    |

| Codirection                                                  |                                     | M,D,P,L,R                                                                                                  | 9             |                                              | 5                    | ns    |

| Channel Matching                                             | <b>t</b> PSKOD                      |                                                                                                            | 9,10,11       |                                              | 9                    | ns    |

| Opposing-Direction                                           |                                     | M,D,P,L,R                                                                                                  | 9             |                                              | 9                    | ns    |

| SUPPLY CURRENT                                               |                                     | LE CAMPOS ACAMPOS OSTADOS                                                                                  | 1 45          |                                              | 1 42                 | Г .   |

| Dynamic Supply                                               | I <sub>DD1(D)</sub>                 | F = 2MBPS, 10MBPS, 25MBPS                                                                                  | 4,5           |                                              | 13                   | mA    |

| Current                                                      |                                     |                                                                                                            | 6             |                                              | 14.5                 | mA    |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 4             |                                              | 13                   | mA    |

|                                                              | $I_{DD2(D)}$                        | F = 2MBPS, 10MBPS, 25MBPS                                                                                  | 4,5           |                                              | 20                   | mA    |

|                                                              |                                     |                                                                                                            | 6             |                                              | 22                   | mA    |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 4             |                                              | 20                   | mA    |

| Quiescent Supply                                             | I <sub>DD1(Q)</sub>                 |                                                                                                            | 1,2,3         |                                              | 2.4                  | mA    |

| Current                                                      |                                     | M,D,P,L,R                                                                                                  | 1             |                                              | 2.4                  | mA    |

|                                                              | $I_{DD2(Q)}$                        |                                                                                                            | 2             |                                              | 2.92                 | mA    |

|                                                              |                                     |                                                                                                            | 1,3           |                                              | 3.5                  | mA    |

| DC CHADACTEDICTICS                                           |                                     | M,D,P,L,R                                                                                                  | 1             |                                              | 3.5                  | mA    |

| DC CHARACTERISTICS  Logic High Input                         | VIH                                 | 7/                                                                                                         | 1 2 2         | 0.71/                                        | I                    | V     |

| Threshold                                                    | VIH                                 | M,D,P,L,R                                                                                                  | 1,2,3         | 0.7 V <sub>DDx</sub><br>0.7 V <sub>DDx</sub> |                      | V     |

| Logic low Input                                              | VIL                                 | 7/                                                                                                         | 1,2,3         | U./ VDDx                                     | 0.3 V <sub>DDx</sub> | V     |

| Threshold                                                    | VIL                                 | M,D,P,L,R                                                                                                  | 1,2,3         |                                              | 0.3 V <sub>DDx</sub> | V     |

| Logic High Output                                            | VOH                                 | $I_{\text{Ox}} = -20 \mu\text{A},  V_{\text{Ix}} = V_{\text{IxH}}  \frac{5}{2},  \frac{6}{2}, \frac{7}{2}$ | 1,2,3         | V <sub>DDx</sub> - 0.1                       | 0.5 V DDx            | V     |

| Voltages                                                     |                                     | M,D,P,L,R                                                                                                  | 1             | V <sub>DDx</sub> - 0.1                       |                      | V     |

| voitages                                                     |                                     | $I_{Ox} = -4 \mu A$ , $V_{Ix} = V_{IxH} 5/, 6/,7/$                                                         | 1,2,3         | $V_{DDx} - 0.1$<br>$V_{DDx} - 0.4$           |                      | V     |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 1,2,3         | $V_{DDx} = 0.4$<br>$V_{DDx} = 0.4$           |                      | V     |

| Logic Low Output                                             | VOL                                 | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{IxL} 5/, 6/,7/$                                                         | 1,2,3         | 7000                                         | 0.1                  | V     |

| Voltages                                                     |                                     | M,D,P,L,R                                                                                                  | 1             |                                              | 0.1                  | V     |

|                                                              |                                     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL} 5/, 6/,7/$                                                        | 1,2,3         |                                              | 0.4                  | V     |

|                                                              |                                     | M,D,P,L,R                                                                                                  | 1             |                                              | 0.4                  | V     |

| Parameter<br>See notes at end of table | Symbol                         | Conditions <u>1</u> /<br>Unless otherwise specified            |           | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------|--------------------------------|----------------------------------------------------------------|-----------|-----------|--------------|--------------|-------|

| Input Leakage Current                  | I <sub>IH</sub>                | $V_{Ix} = V_{DDx} 5/, 6/,7/$                                   |           | 1,2,3     | -10          | +10          | μΑ    |

| per Channel                            |                                |                                                                | M,D,P,L,R | 1         | -10          | +10          | μΑ    |

|                                        | I <sub>IL</sub>                | $V_{lx} = 0V \ \underline{5}/, \underline{6}/, \underline{7}/$ |           | 1,2,3     | -10          | +10          | μΑ    |

|                                        |                                |                                                                | M,D,P,L,R | 1         | -10          | +10          | μΑ    |

| AC CHARACTERISTICS                     |                                |                                                                |           |           |              |              |       |

| Output Rise/Fall Time                  | t <sub>R</sub> /t <sub>F</sub> | 10% to 90%                                                     |           | 4         |              | 3.5          | ns    |

| <u>2</u> /, <u>3</u> /                 |                                |                                                                |           | 5         |              | 4.5          |       |

|                                        |                                |                                                                |           | 6         |              | 3            | 1     |

#### TABLE ID NOTES:

- $1/T_{A}$  nom = 25°C,  $T_{A}$  max = 125°C, and  $T_{A}$  min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted.  $V_{DD1}$  nom = 3.3 V,  $V_{DD1}$  max = 3.6V,  $V_{DD1}$  min = 3V /  $V_{DD2}$  nom = 5 V,  $V_{DD2}$  max = 5.5V,  $V_{DD2}$  min = 4.5V.

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation.

- 4/ t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ V<sub>Ix</sub> refers to the voltage input signals of a given channel (A, B, C, or D).

- 6/ lox refers to the output current of a given channel (A, B, C, or D).

- 7/ V<sub>DDx</sub> refers to the power supply on either side of a given channel (A, B, C, or D).

#### TABLE IE – ELECTRICAL PERFORMANCE CHARACTERISTICS- INSULATION AND SAFETY-RELATED SPECIFICATIONS

| Parameter                                                                                   | Symbol           | Value            | Unit  | Conditions                                                                    |

|---------------------------------------------------------------------------------------------|------------------|------------------|-------|-------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage $\underline{1}$ /, $\underline{2}$ /, $\underline{3}$ / | lso              | 200              | Vpeak | 1-minute duration                                                             |